Next: Signal gating with filler

Up: Interconnect-aware Low Power High-level

Previous: Communication-sensitive binding

Reducing Spurious Switching Activity

Signal gating (a.k.a operand isolation) based

power management has been used to freeze the inputs to a DPU to

suppress SSA [1,36,61]. The same idea can be

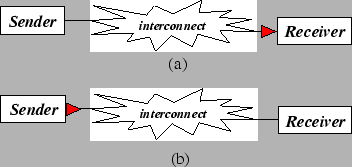

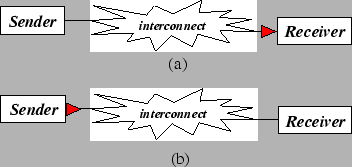

used for interconnects as well. The difference is shown in

Fig. 8. Traditional signal gating is placed

before the DPU that receives the signal ( , at the

receiver)as shown in Fig. 8(a), while our

approach gates the signal right after the source (

, at the

receiver)as shown in Fig. 8(a), while our

approach gates the signal right after the source ( , at the

sender)as shown in Fig. 8(b).

, at the

sender)as shown in Fig. 8(b).

Figure 8:

Signal gating

(a) before the DPU and

(b) before the interconnect.

|

The gating mechanism decides whether data can propagate through

the gating logic or not. Interconnect-aware power management gates

a signal with SSA before it propagates onto the output network.

When the controller is properly respecified [37], it also

reduces SSA in the downstream DPUs. In this section, we propose

implementations for the gating mechanism. The methods we propose

next are relatively independent of the high-level synthesis

process. Thus, they can be applied as a post-processing step after

high-level synthesis,  , the resultant RTL architecture can

be further optimized with these methods even if the architecture

is obtained by some other high-level synthesis system.

, the resultant RTL architecture can

be further optimized with these methods even if the architecture

is obtained by some other high-level synthesis system.

Subsections

Next: Signal gating with filler

Up: Interconnect-aware Low Power High-level

Previous: Communication-sensitive binding

Lin Zhong

2003-10-11